### **DATA SHEET**

# **NVIDIA Jetson Orin Nano Series**

Ampere GPU + ARM Cortex-A78AE CPU + LPDDR5

#### **NVIDIA Jetson Orin Nano Modules:**

- Jetson Orin Nano 8GB (ON 8GB) Ampere GPU + ARM Cortex-A78AE CPU + 8GB LPDDR5

- Jetson Orin Nano 4GB (ON 4GB) Ampere GPU + ARM Cortex-A78AE CPU + 4GB LPDDR5

References to ON and Jetson Orin Nano can be read as Jetson Orin Nano 8GB and Jetson Orin Nano 4GB except where explicitly noted.

#### **Al Performance**

Jetson Orin Nano 8GB: Up to 40 (Sparse) INT8 TOPs and 20 (Dense) INT8 TOPs

Jetson Orin Nano 4GB: Up to 20 (Sparse) INT8 TOPs and 10 (Dense) INT8 TOPs

### **Ampere GPU**

Jetson Orin Nano 8GB: 1024 NVIDIA® CUDA® cores | 32 Tensor cores

Jetson Orin Nano 4GB: 512 NVIDIA® CUDA® cores | 16 Tensor cores

End-to-end lossless compression | Tile Caching | OpenGL® 4.6 |

OpenGL ES 3.2 | Vulkan M 1.1° | CUDA 10

Maximum Operating Frequency: 625 MHz

#### **ARM Cortex-A78AE CPU**

Six-core (ON 8GB and ON 4GB) Cortex A78AE ARMv8.2 (64-bit) heterogeneous multi-processing (HMP) CPU architecture | 2x clusters (1x 4-core cluster + 128 KB L1 + 256KB L2 per core + 2MB L3) + 1x 2-core cluster (128 KB L1 + 256KB L2 per core + 2MB L3) | System Cache: 4 MB (shared across all clusters)

#### Audio

Dedicated programmable audio processor | ARM Cortex A9 with NEON | PDM in/out | Industry-standard High-Definition Audio (HDA) controller provides a multi-channel audio path to the HDMI® interface

#### Memory

ON 8GB: 8GB 128-bit LPDDR5 DRAM ON 4GB: 4GB 64-bit LPDDR5 DRAM

Secure External Memory Access Using TrustZone® Technology | System MMU | Maximum Operating Frequency: 2133 MHz

#### Networking

10/100/1000 BASE-T Ethernet | Media Access Controller (MAC)

#### **Imaging**

Eight lanes MIPI CSI-2 | D-PHY 2.1 (20 Gbps)

#### **Display Controller**

1x4K30 DP 1.2 (+MST for 2x 1080p60), HDMI 1.4, eDP 1.4

\*See the Display section for more details on additional compatibility to DP 1.4a and HDMI 2.1

Maximum Resolution (eDP/DP/HDMI): up to 3840x2160 at 30 Hz

#### Multi-Stream HD Video and JPEG

Video Decode:

- Standards supported: H.265 (HEVC), H.264, VP9, AV1

- o 1x4K60 (H.265)

- o 2x4K30 (H.265)

- o 5x1080p60 (H.265)

- o 11x1080p30 (H.265)

Video Encode:

1080p30 Supported via CPU Cores with Software

### Peripheral Interfaces

xHCl host controller with integrated PHY (up to) 3x USB 3.2, 3x USB 2.0 | 3 x1 (or 1 x2 + 1 x1) + 1 x4 (GEN3) PCIe | 3x UART | 2x SPI | 4x  $I^2C$  | 1x CAN | DMIC | DSPK | 2x  $I^2S$  | 15x GPIOs

#### Storage

Supports External Storage (for example: NVMe)

#### Mechanical

Module Size: 69.6 mm x 45 mm | 260 pin SO-DIMM Connector

#### **Operating Requirements**

Temp. Range  $(T_J)^*$ : -25°C – 90°C | Supported Power Input: 5V

Jetson Orin Nano 8GB Modes: 7W | 15W Jetson Orin Nano 4GB Modes: 7W | 10W

Note: Refer to the Software Features section of the latest L4T Development Guide for a list of supported features; all features may not be available.

- Product is based on a published Khronos Specification and is expected to pass the Khronos Conformance Process. Current conformance status can be found at <a href="https://www.khronos.org/conformance">www.khronos.org/conformance</a>.

- \* See the future Jetson Orin Nano Thermal Design Guide for details.

# **Revision History**

| Version | Date               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v0.1    | September 20, 2022 | Initial preliminary release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| v0.2    | December 5, 2022   | <ul> <li>Updated:         <ul> <li>Supported External Storage for clarity.</li> <li>Supported Power Input for Operating Requirements.</li> <li>Compute performance for (S) INT8 TOPs and (D) INT8 TOPs in Functional Overview for clarity.</li> <li>VDD_IN pin type in Power and System Control Pin Descriptions table.</li> <li>MODULE_ID description in Power and System Control Pin Descriptions table.</li> <li>VDD_IN parameter to only support 5V Input Voltage in Recommended Operating Conditions table.</li> </ul> </li> <li>Removed:         <ul> <li>AV1 Decode Maximum Aggregate Mbps, correct breakdown in Supported</li> </ul> </li> </ul> |

| v1.0    | February 22, 2023  | <ul> <li>Video Decode Streams table.</li> <li>Updated: <ul> <li>Minimum power ratings for Operating Requirements.</li> <li>USB 3.2 Operation text for clarification.</li> <li>Pin description for SYS_RESET* to 10kΩ pull-up to VDD_1V8 on the module.</li> <li>Pin description for CLK_32K_OUT to 2.2kΩ pull-up to VDD_1V8 on the module.</li> <li>PMIC_BBAT Pin Description table for clarity.</li> </ul> </li> <li>Added: <ul> <li>Absolute Maximum Ratings table.</li> <li>Storage and Handling table.</li> <li>Environmental Testing table.</li> </ul> </li> </ul>                                                                                  |

| v1.1    | April 26, 2023     | Added:  Note for internal USB 3.2 hub. Added package drawing information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### **Table of Contents**

| 1.0 | ) Functional Overview                                          | 5                     |

|-----|----------------------------------------------------------------|-----------------------|

|     | 1,1 Ampere GPU                                                 | 5                     |

|     | 1.1.1 Compute Features                                         |                       |

|     | 1.1.2 Graphic Features                                         |                       |

|     | 1.1.3 GPU Architecture                                         |                       |

|     | 1.2 Cortex CPU Complex                                         |                       |

|     | 1.3 Memory Subsystem                                           |                       |

|     | 1.4 Memory                                                     |                       |

|     | 1.5 Video Input Interfaces                                     | 8                     |

|     | 1.5.1 MIPI Camera Serial Interface (CSI)                       |                       |

|     | 1.5.2 Video Input (VI)                                         | 10                    |

|     | 1.5.3 Image Signal Processor (ISP)                             | 10                    |

|     | 1.6 Sensor Processing Engine                                   |                       |

|     | 1.7 Security Subsystem                                         |                       |

|     | 1.7.1 Platform Security Controller                             |                       |

|     | 1.7.2 Security Engine                                          |                       |

|     | 1.8 Display Controller                                         |                       |

|     | 1.9 High-Definition Audio-Video Subsystem                      |                       |

|     | 1.9.1 Multi-Standard Video Decoder                             |                       |

|     | 1.9.2 Video Image Compositor (VIC)                             | 14                    |

|     | 1.9.3 Audio Processing Engine (APE)                            | 15                    |

|     | 1.9.4 High-Definition Audio (HDA)                              |                       |

|     | 1.10 Interface Descriptions                                    |                       |

|     | 1.10.1 Universal Serial Bus (USB)                              |                       |

|     | 1.10.2 PCI Express (PCIe)                                      |                       |

|     | 1.10.3 Serial Peripheral Interface (SPI)                       | ۱۶<br>۲۰              |

|     | 1.10.5 Controller Area Network (CAN)                           | ∠∪<br>21              |

|     | 1.10.6 Inter-Chip Communication (I <sup>2</sup> C)             | ر کے<br>22            |

|     | 1.10.7 Inter-IC Sound (I <sup>2</sup> S)                       |                       |

|     | 1.10.8 Gigabit Ethernet                                        |                       |

|     | 1.10.9 Fan                                                     |                       |

|     | 1.10.10 Pulse Width Modulator (PWM)                            |                       |

| 2 0 |                                                                | 25                    |

| 2.0 | Power and System Management                                    |                       |

|     | 2.1 Power Rails                                                |                       |

|     | 2.2 Power Domains/Islands                                      |                       |

|     | 2.3 Power Management Controller (PMC)                          |                       |

|     | 2.4 Resets                                                     |                       |

|     | 2.5 PMIC_BBAT                                                  |                       |

|     | 2.6 Power Sequencing                                           | 26                    |

|     | 2.6.1 Power Up                                                 |                       |

|     | 2.6.2 Power Down                                               |                       |

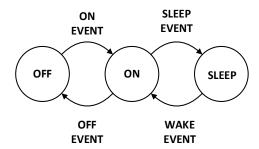

|     | 2,7 Power States                                               |                       |

|     | 2.7.1 ON State                                                 |                       |

|     | 2.7.2 OFF State                                                |                       |

|     | 2.8 Thermal and Power Monitoring                               |                       |

|     | •                                                              |                       |

| 3.0 | ) Pin Definitions                                              | 29                    |

|     | 3.1 Power-on Reset Behavior                                    |                       |

|     | 3.2 Sleep Behavior                                             |                       |

|     | 3.3 GPIO                                                       |                       |

|     | 3.4 Jetson Orin Nano Pin List                                  | 31                    |

|     |                                                                |                       |

| 4.0 | DC Characteristics                                             | 34                    |

| 4.0 | DC Characteristics                                             | 34                    |

| 4.0 | DC Characteristics  4.1 Operating and Absolute Maximum Ratings | <b>34</b><br>34<br>35 |

| 4.0 | DC Characteristics 4.1 Operating and Absolute Maximum Ratings  | <b>34</b><br>34<br>35 |

| 5.0 Environmental and Mechanical Screening | 36 |

|--------------------------------------------|----|

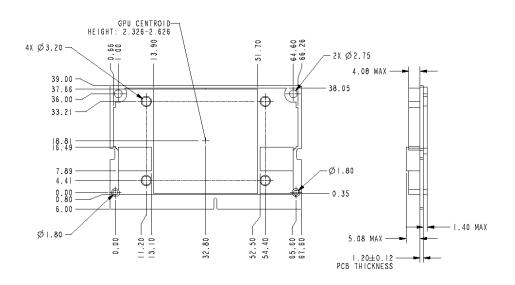

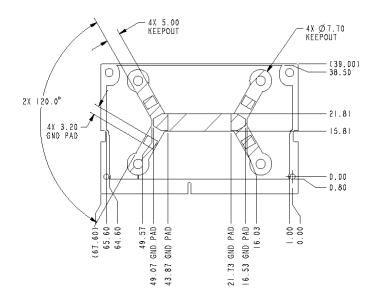

| 6.0 Package Drawing and Dimensions         | 37 |

### 1.0 Functional Overview

The NVIDIA® Jetson Orin™ Nano brings AI supercomputer performance to the edge in a compact system-on-module (SOM) which is smaller than a credit card. Jetson Orin Nano is built around a low-power version of the NVIDIA Orin SoC, combining the NVIDIA Ampere™ GPU architecture with 64-bit operating capability, integrated advanced multi-function video and image processing, and NVIDIA Deep Learning Accelerators.

Compute performance up to 40 (Sparse) INT8 TOPs and 20 (Dense) INT8 TOPs on the Jetson Orin Nano 8GB and up to 20 (S) INT8 TOPs and 10 (D) INT8 TOPs on the Jetson Orin Nano 4GB enables these modules to run multiple neural networks in parallel and process data from multiple high-resolution sensors simultaneously. It also offers a unique combination of performance and power advantages with a rich set of I/Os, from high-speed CSI and PCIe to low-speed I<sup>2</sup>Cs and GPIOs, allowing embedded and edge computing devices that demand increased performance but are constrained by size, weight, and power budgets.

# 1.1 Ampere GPU

The NVIDIA Ampere GPU introduces a new design for the Streaming Multiprocessor (SM) that dramatically improves performance per watt and performance per area, along with supporting Tensor Cores and TensorRT cores. Ampere GPUs improve on the previous NVIDIA Turing™ generation; and are software compatible so that the same APIs are used.

The NVIDIA Ampere Architecture GPU has several enhancements for compute and graphics capability that include:

- Sparsity: fine grained structured sparsity doubles throughput and reduces memory usage.

- 2x CUDA floating-point performance: higher compute math speed.

- SM architecture improves bandwidth to the L1 cache and shared memory and reduces L1 miss latency.

- Improved async compute, and post-L2 cache compression compared to NVIDIA Turing.

## 1.1.1 Compute Features

Ampere introduces third-generation NVIDIA Tensor Cores which offer a wider range of precisions including TensorFloat-32 (TF32), bfloat16, FP16, and INT8 all of which provide unmatched versatility and performance.

TensorFloat-32 (TF32) is a new format that uses the same 10-bit Mantissa as half-precision (FP16) math and is shown to have more than sufficient margin for the precision requirements of AI workloads. In addition, since the TF32 adopts the same 8-bit exponent as FP32 it can support the same numeric range.

Ampere adds support for structured sparsity. Not all the parameters of modern AI networks are needed for accurate predictions and inference, and some can be converted to zeros to make the models "sparse" without compromising accuracy. The Tensor Cores in Ampere can provide up to 2x higher performance for inference of sparse models.

Ampere supports Compute Data Compression which can accelerate unstructured sparsity and other compressible data patterns. Compression in L2 provides up to a 4x improvement in DRAM read/write bandwidth, up to 4x improvement in L2 read bandwidth, and up to a 2x improvement in L2 capacity.

Ampere also supports many other enhancements for higher compute throughput.

**Table 1: GPU Operation**

| Module               | CUDA Cores | Tensor Cores | Operating Frequency per Core (up to) |

|----------------------|------------|--------------|--------------------------------------|

| Jetson Orin Nano 8GB | 1024       | 32           | 625 MHz                              |

| Jetson Orin Nano 4GB | 512        | 16           | 625 MHz                              |

# 1.1.2 Graphic Features

Ampere graphics capabilities include:

- End-to-end lossless compression, including Post-L2 compression, enabling compression of M stores.

- Tiled Caching

- OpenGL 4.6+, Vulkan 1.2+, CUDA 10.2+

- Adaptive Scalable Texture Compression (ASTC) LDR profile supported

- Modern Graphics features:

- Ray Tracing

- DL Inferencing

- Mesh Shaders

- Sampler Feedback

- Variable Rate Shading

- Texture LOD in compute programs

- Iterated blend, ROP OpenGL-ES blend modes

- 2D BLIT from 3D class avoids channel switch

- 2D color compression

- Constant color render SM bypass

- 2x, 4x, 8x MSAA with color and Z compression

- Non-power-of-2 and 3D textures, FP16 texture filtering

- FP16 shader support

- Geometry and Vertex attribute Instancing

- Parallel pixel processing

- Early-z reject: Fast rejection of occluded pixels acts as multiplier on pixel shader andtexture performance while saving power and bandwidth

- Video protection region

### 1.1.3 GPU Architecture

There are multiple texture processing clusters (TPC) units within a graphics processing cluster (GPC), each TPC includes two SMs, a Polymorph Engine, two Texture Units, and a RayTracing core (RTcore). Each GPC includes a Raster Engine (ROP), which can access all of memory. Each SM is partitioned into four separate processing blocks, each with its own instruction buffer, scheduler and 128 CUDA cores.

The GPC is a dedicated hardware block for rasterization, shading, texturing, and compute. The GPU's core graphics functions are performed inside the GPC. Inside the GPC, the SM CUDA cores perform pixel/vertex/geometry shading and physics/compute calculations. Texture unitsperform texture filtering and load/store units fetch and save data to memory. Special Function Units (SFUs) handle transcendental and graphics interpolation instructions. Tensor cores perform matrix multiplies to greatly accelerate DL inferencing. The RTcore unit assists Ray Tracing by accelerating Bounding Volume Hierarchy (BVH) traversal and intersection of scene geometry during Ray Tracing.

Finally, the PolyMorph engine handles vertex fetch, tessellation, viewport transform, attribute setup, and stream output. The SM geometry and pixel processing performance make it highlysuitable for rendering advanced user interfaces and complex gaming applications. The power efficiency of the Ampere GPU enables this performance on devices with power-limited environments.

# 1.2 Cortex CPU Complex

The CPU cluster is comprised of six cores of ARM Cortex-A78AE Core processors organized as one quad-core clusters, and one dual-core cluster. Clusters contain private L1 and L2 caches per core, a Snoop Control Unit (SCU), and a cluster-level L3 cache (shared by the four cores), an interconnect fabric and debug support modules (CoreSight).

#### Features:

- Superscalar, variable-length, out-of-order pipeline.

- Dynamic branch prediction with Branch Target Buffer (BTB) and a branch direction predictor using previous branch history, a return stack, a static predictor, and an indirect predictor.

- A 1.5K entry, 4-way skewed associative L0 Macro-OP (MOP) cache.

- 32-entry fully-associative L1 instruction TLB with native support for 4KB, 16KB, 64KB, and 2MB page sizes.

- 32-entry fully-associative L1 data TLB with native support for 4KB, 16KB, 64KB, 2MB, and 512MB page sizes.

- 4-way set-associative unified 1024-entry Level 2 (L2) TLB in each processor.

- L1 caches separate 64 KB I-cache and 64 KB D-cache for each core.

- L2 cache a unified, 8-way set associative, 256 KB L2 cache per core.

- 40-bit Physical Address (PA)

#### Cortex-A78AE CPU supports:

- Full implementation of ARMv8.2-A architecture instruction set and select instructions from ARMv8.3-A, ARMv8.4-A, and ARMv8.5-A extensions.

- Embedded Trace Microcell (ETM) based on the ETMv4.2 architecture.

- Performance Monitor Unit (PMU) based on the PMUv3 architecture.

- CoreSight for debugging based on CoreSightv3 architecture.

- Cross Trigger Interface (CTI) for multiprocessor debugging.

- Generic Timer Interface based on ARMv8-A architecture and 64-bit count input from external system counter.

- Cryptographic Engine for crypto function support.

- Interface to an external Generic Interrupt Controller based on GICv3 architecture.

- Power management with multiple power domains.

### **Table 2: CPU Operation**

| Module        | CPU Cores | CPU Maximum Frequency |

|---------------|-----------|-----------------------|

| Orin Nano 8GB | 6         | 1.5 GHz               |

| Orin Nano 4GB | 6         | 1.5 GHz               |

# 1.3 Memory Subsystem

8GB 128-bit LPDDR5 DRAM is used on the Jetson Orin Nano 8GB, and 4GB 64-bit LPDDR5 DRAM is used in the Jetson Orin Nano 4GB. It supports the following:

- Secure external memory access using TrustZone technology

- System MMU

- Maximum operating frequency: 2133 MHz

The Memory Subsystem (MSS) provides access to local DRAM, SysRAM, and provides a SyncPoint Interface for interprocessor signaling. The MSS supports full-speed I/O coherence by routing requests through a scalable coherence fabric. It also supports a comprehensive set of safety and security mechanisms.

### Structurally, the MSS consists of:

- 1 MSS Data Backbone routes requests from clients to the MSS Hub and responses from MSS Hub to the clients.

- 2 MSS Hub receives and arbitrates among client requests, performs SMMU translation, and sends requests to MCF.

- 3 Memory Controller Fabric (MCF) performs security checks, feeds I/O coherent requests to the Scalable Coherence Fabric (SCF), and directs requests to the multiple memory channels.

- 4 Memory Controller (MC) Channels row sorter/arbiter and DRAM controllers.

- 5 DRAM I/O channel-to-pad fabric, DRAM I/O pads, and PLLs.

Jetson Orin Nano provides three independent column address bits to each sub-partition, allowing it access different 32-byte sectors of a Group of Bytes (GOB) between the sub-partitions. It provides connections between a wide variety of clients, supporting their bandwidth, latency, quality-of-service needs, and any special ordering requirements that are needed. The MSS supports a variety of security and safety features and address translation for clients that use virtual addresses.

#### Features:

- LPDDR5

- 64-bit or 128-bit wide data bus

- Low latency path and fast read/response path support for the CPU complex cluster

- Support for low-power modes:

- o Software controllable entry/exit from self-refresh, power down, and deep power down

- Hardware dynamic entry/exit from power down, self-refresh

- Pads use DPD mode during idle periods

- High-bandwidth interface to the integrated Ampere GPU

- Full-speed I/O coherence with bypass for Isochronous (ISO) traffic

- System Memory-Management Unit (SMMU) for address translation based on the ARM SMMU-500

- High-bandwidth PCIe ordered writes

- AES-XTS encryption with 128-bit key

# 1.4 Memory

The Jetson Orin Nano 8GB integrates 8GB 128-bit LPDDR5 DRAM, and Jetson Orin Nano 4GB integrates 4GB 64-bit LPDDR5 DRAM. Maximum frequency of Jetson Orin Nano Memory is 2133 MHz. The theoretical peak memory bandwidth on Orin Nano 8GB is 68 GB/s, and on Orin Nano 4GB is 34 GB/s.

The Memory Controller (MC) maximizes memory utilization while providing minimum latency access for critical CPU requests. An arbiter is used to prioritize requests, optimizing memory access efficiency and utilization and minimizing system power consumption. The MC provides access to main memory for all internal devices. It provides an abstract view of memory to its clients via standardized interfaces, allowing the clients to ignore details of the memory hierarchy. It optimizes access to shared memory resources, balancing latency and efficiency to provide best system performance, based on programmable parameters.

#### Features:

- TrustZone (TZ) Secure and OS-protection regions

- System Memory Management Unit

- Dual CKE signals for dynamic power down per device

- Dynamic Entry/Exit from Self-Refresh and Power Down states

# 1.5 Video Input Interfaces

# 1.5.1 MIPI Camera Serial Interface (CSI)

### **Standard**

MIPI CSI 2.0 Receiver specification

MIPI D-PHY® 2.1 Physical Layer specification

The NVIDIA Camera Serial Interface (NVCSI) works with the Video Input (VI) unit to capture an image from a sensor, where NVCSI is a source of pixel data to VI. NVCSI works in streaming mode while VI captures the required frames using a single-shot mode of operation. All sync point generation for software is handled at VI; the delay between NVCSI and VI is negligible in software terms. NVCSI does not have a direct memory port, instead it sends the pixel data to memory through the VI.

Fifth-generation NVIDIA camera solution (NVCSI 2.0, VI 5.0, and ISP 6.x) provides a combination host that supports enhanced MIPI D-PHY (with lane deskew support) physical layer options in two 4-lane or four 2-lane configurations; or combinations of these. Orin Nano can support up to 16 virtual channels (VC) and supports data type interleaving.

- Virtual Channel Interleaving: VCs are defined in the CSI-2 specification and are useful when supporting multiple camera sensors. With the VC capability, a one-pixel parser (PP) can de-interleave up to 16 image streams.

- Data Type Interleaving: In HDR line-by-line mode, the sensor can output long/short exposure lines using the same VC and a different programmable data type (DT).

- Frequency Target: The parallel pixel processing rate, measured in pixels-per-clock (PPC), is increased to allow higher throughput and lower clock speeds. To support higher bandwidth without increasing the operating frequency, the host processes multiple pixels in one clock. NVCSI is capable of processing four PPCs when bits-per-pixel (BPP) is greater than 16, and eight PPC when BPP is less than or equal to 16.

- With the new streaming mode in NVCSI, one PP can handle all traffic (embedded data and image data) from one camera device, including 16 VCs.

#### Features:

- Supports the MIPI D-PHY v2.1 physical layer option:

- MIPI D-PHY supports up to 2.5 Gbits/sec per pair, for an aggregate bandwidth of 20 Gbps from eight pairs

- Based on MIPI CSI-2 v3.0 protocol stack

- Includes six-pixel parsers (PP)

- Supports up to 16 virtual channels

- Supported input data formats:

- o RGB: RGB888, RGB666, RGB565, RGB555, RGB444

- o YUV: YUV420-8b (legacy), YUV420-8b

- o RAW: RAW6, RAW7, RAW8, RAW10, RAW12, RAW14, RAW16,

- Data Type Interleave support

#### **Table 3: CSI Pin Descriptions**

| Pin# | Signal Name       | Description           | Direction | Pin Type   |

|------|-------------------|-----------------------|-----------|------------|

| 10   | CSI0_CLK_N        | Camera, CSI 0 Clock-  | Input     | MIPI D-PHY |

| 12   | CSI0_CLK_P        | Camera, CSI 0 Clock+  | Input     | MIPI D-PHY |

| 4    | CSI0_D0_N         | Camera, CSI 0 Data 0- | Input     | MIPI D-PHY |

| 6    | CSI0_D0_P         | Camera, CSI 0 Data 0+ | Input     | MIPI D-PHY |

| 16   | CSI0_D1_N         | Camera, CSI 0 Data 1- | Input     | MIPI D-PHY |

| 18   | CSI0_D1_P         | Camera, CSI 0 Data 1+ | Input     | MIPI D-PHY |

| 9    | RSVD (CSI1_CLK_N) | Camera, CSI 1 Clock-  | Input     | MIPI D-PHY |

| 11   | RSVD (CSI1_CLK_P) | Camera, CSI 1 Clock+  | Input     | MIPI D-PHY |

| 3    | CSI1_D0_N         | Camera, CSI 1 Data 0- | Input     | MIPI D-PHY |

| 5    | CSI1_D0_P         | Camera, CSI 1 Data 0+ | Input     | MIPI D-PHY |

| 15   | CSI1_D1_N         | Camera, CSI 1 Data 1- | Input     | MIPI D-PHY |

| 17   | CSI1_D1_P         | Camera, CSI 1 Data 1+ | Input     | MIPI D-PHY |

| 28   | CSI2_CLK_N        | Camera, CSI 2 Clock-  | Input     | MIPI D-PHY |

| 30   | CSI2_CLK_P        | Camera, CSI 2 Clock+  | Input     | MIPI D-PHY |

| 22   | CSI2_D0_N         | Camera, CSI 2 Data 0- | Input     | MIPI D-PHY |

| Pin # | Signal Name | Description           | Direction | Pin Type   |

|-------|-------------|-----------------------|-----------|------------|

| 24    | CSI2_D0_P   | Camera, CSI 2 Data 0+ | Input     | MIPI D-PHY |

| 34    | CSI2_D1_N   | Camera, CSI 2 Data 1- | Input     | MIPI D-PHY |

| 36    | CSI2_D1_P   | Camera, CSI 2 Data 1+ | Input     | MIPI D-PHY |

| 27    | CSI3_CLK_N  | Camera, CSI 3 Clock-  | Input     | MIPI D-PHY |

| 29    | CSI3_CLK_P  | Camera, CSI 3 Clock+  | Input     | MIPI D-PHY |

| 21    | CSI3_D0_N   | Camera, CSI 3 Data 0- | Input     | MIPI D-PHY |

| 23    | CSI3_D0_P   | Camera, CSI 3 Data 0+ | Input     | MIPI D-PHY |

| 33    | CSI3_D1_N   | Camera, CSI 3 Data 1– | Input     | MIPI D-PHY |

| 35    | CSI3_D1_P   | Camera, CSI 3 Data 1+ | Input     | MIPI D-PHY |

**Table 4: Camera Pin Descriptions**

| Pin # | Signal Name | Description                | Direction | Pin Type    |

|-------|-------------|----------------------------|-----------|-------------|

| 116   | CAM0_MCLK   | Camera 0 Reference Clock   | Bidir     | CMOS – 1.8V |

| 114   | CAM0_PWDN   | Camera 0 Powerdown or GPIO | Bidir     | CMOS – 1.8V |

| 122   | CAM1_MCLK   | Camera 1 Reference Clock   | Bidir     | CMOS – 1.8V |

| 120   | CAM1_PWDN   | Camera 1 Powerdown or GPIO | Bidir     | CMOS – 1.8V |

# 1.5.2 Video Input (VI)

The VI block receives data from the CSI receiver and prepares it for presentation to system memory or the dedicated image signal processor execution resources. The VI block provides formatting for RGB, YCbCr, and raw Bayer data in support of several camera user models. These models include single and multi-camera systems, which may have up to six active streams. The input streams are obtained from MIPI compliant CMOS sensor camera modules.

# 1.5.3 Image Signal Processor (ISP)

The ISP module takes data from the VI/CSI module or memory in raw Bayer format and processes it to YUV output. The imaging subsystem supports raw (Bayer) image sensors up to 10 million pixels. Advanced image processing is used to convert input to YUV data and remove artifacts introduced by high-megapixel CMOS sensors and optics with up to 30-degree CRA.

The ISP in the Jetson Orin Nano supports a maximum frequency of 704 MHz, with two pixels/clock is equivalent to approximately 1408 MPixels.

### Features:

- Flexible post-processing architecture for supporting custom computer vision and computational imaging operations.

- Hardware noise reduction

- Black-level compensation

- Lens-shading compensation

- · Bad pixel correction

- Edge enhancement

- Color and gamma correction

- Global and local tone mapping

- Color-space conversion (RGB to YUV)

# 1.6 Sensor Processing Engine

The Cortex-R5 processor in the Always On (AON) block is also referred to as the Sensor Processing Engine (SPE). The AON cluster provides all the necessary hardware features to support low power sensor management and wake use cases. The cluster consists of an Arm Cortex-R5 processor core with a tightly coupled RAM, supporting peripherals (such as timers and an interrupt controller), various I/O controller peripherals, and routing logic.

AON Cortex-R5 implementation:

- Arm v7-R ISA

- Integrated instruction and data caches

- Tightly coupled memory (TCM) interface for local SRAM

- Vectored interrupt support

- 64-bit AXI Initiator interface for DRAM requests

- 32-bit AXI Initiator interface for MMIO requests

- 32-bit AHB Initiator interface for Arm Vectored Interrupt Controller (AVIC) access

- · AXI Target interface for DMA access to the local SRAM

# 1.7 Security Subsystem

This subsystem is comprised of the following:

- Platform Security Controller (PSC)

- Security Engine (SE)

### 1.7.1 Platform Security Controller

The Platform Security Controller (PSC) is a highly secure subsystem to protect and manage assets (keys, fuses, functions, and features) within the SoC, provide trusted services, increase resilience against attacks on the SoC, and provide a greater level of protection against software and hardware attacks on the subsystem itself.

**Key Management and Protection:** The PSC will be the only mechanism with access to the most critical secrets in the chip. This subsystem represents the highest level of protection in Orin and the subsystem itself is highly resilient to a wide range of software and hardware attacks.

**Trusted Services:** The primary PSC services include secure authentication (for example, during SoC secure boot), provisioning of additional keys, ID, data, key access and management, random number generation, and trusted time reporting.

**Security Monitor:** The PSC will be responsible for periodic security housekeeping tasks, including continually assessing the security status of the SoC, actively monitor known or potential attack patterns (for example, such as voltage glitching or thermal attacks), mitigate hardware attack risks, and to take action in the case of a detected attack. The PSC will have the ability to accept updates as workarounds to improve the robustness of the system in the field.

# 1.7.2 Security Engine

The Security Engine (SE) provides hardware acceleration for cryptographic algorithms. There are two instances of SE available for software usage:

- TZ-SE: accessible only by TrustZone software

- NS/TZ-SE: configurable to be accessible only by TrustZone software or TrustZone and non-secure software

The SE provides hardware acceleration for various cryptographic operations and hardware assisted Key protection. The crypto operations that the SE provides can be used by software to build crypto protocols and security features. All of these crypto operations are based on Crypto algorithms approved by the National Institute of Standards and Technology (NIST).

The SE supports the following:

- NIST-compliant asymmetric, symmetric cryptography and hashing

- Side channel countermeasures [AES/RSA/ECC]

- Independent channels for parallelization

- Hardware Key Access Controls (KAC): Rule-based, hardware-enforced access control for symmetric keys

- 16× AES, 4× RSA/ECC key slots

- Hardware key isolation (only AES keyslots)

- · Read protection (only AES keyslots)

- · Hardware keyslot functions

- Key wrap and unwrap functionality (AES -> AES keyslot)

- Key derivation into a keyslot (KDF -> AES keyslot)

- Random key generation (RNG -> AES keyslot)

## 1.8 Display Controller

The NVIDIA Jetson Orin Nano provides 1x HDMI and DP port. The HDMI and DisplayPort (DP) interfaces share the same set of interface pins.

The Jetson Orin Nano maximum pixel clock is 388 MHz. 4K@30fps is an example of a resolution that can still be supported with this pixel clock. However, resolutions which require a pixel clock higher than 388 MHz (e.g., 4k@60) cannot be supported. It can support DP 1.2, HDMI 1.4, and eDP 1.4.

Due to the above pixel clock, Jetson Orin Nano will not be able to get official DP/HDMI certification for DP 1.4a and HDMI 2.1. However, software/hardware are still compatible with all other parts of the DP1.4a and HDMI2.1 specs listed below.

HDMI provides a unified method of transferring both audio and video data. The HDMI block receives video from either display controller and audio from a separate high-definition audio (HDA) controller; it combines and transmits them as appropriate.

Supported HDMI features are:

- Compliant to the HDMI 1.4 Specification

- Compatible with HDMI 2.1 Specification

- HDCP 2.2

- On-chip HDCP key storage, no external SecureROM required

- Multichannel audio from HDA controller, up to eight channels 192 kHz 24-bit

- 24-bit RGB and 24-bit YUV444 (HDMI) pixel formats

DisplayPort (DP) is a digital display interface often used to connect a video source to a display device over a cable, in consumer or commercial applications.

For embedded use cases that require multiple display support using MST, DP is intended to interface with SerDes devices that in turn supports up to four displays.

Supported DisplayPort features are:

- Compliant to the DisplayPort 1.2 Specification

- Compatible to the DisplayPort 1.44 Specification

- o Support 16 bpp YUV422

- Support 18 bpp RGB

- Support 24 bpp RGB/YUV444

- Support 30 bpp RGB/YUV444

- Support 36 bpp RGB/YUV444

- Support up to 388 MHz pixel clock

- Support for 1/2/4 lanes

- Support for following bit rates:

- o RBR (Reduced Bit Rate, 1.62 Gbps)

- o HBR (High Bit Rate, 2.7 Gbps)

- HBR2 (High Bit Rate 2, 5.4 Gbps)

- o HBR3 (High Bit Rate 3, 8.1 Gbps)

- Multi-Stream Transport (MST)

- Support for 2-8 channel audio streaming up to 96 kHz sample rate

- Support additional eDP 1.4 features:

- o Additional link rates (2.16, 2.43, 3.24, 4.32 Gbps)

- Enhanced framing

- Power sequencing

- o Reduced AUX timing

- o Reduced main voltage swing

- o Alternate Seed Scrambler Reset (ASSR) for internal eDP panels

# 1.9 High-Definition Audio-Video Subsystem

### **Standard**

High-Definition Audio Specification Version 1.0a

The HD Audio-Video Subsystem uses a collection of functional blocks to off-load audio and video processing activities from the CPU complex, resulting in fast, fully concurrent, and highly efficient operation. This subsystem is comprised of the following:

- · Multi-standard video decoder

- Video Image Compositor (VIC)

- Audio Processing Engine (APE)

- High-Definition Audio (HDA)

### 1.9.1 Multi-Standard Video Decoder

The Jetson Orin Nano incorporates the NVIDIA Multi-Standard Video Decoder (NVDEC). This video decoder accelerates video decode, supporting low resolution mobile content, Standard Definition (SD), High Definition (HD) and UltraHD (8K, 4K, etc.) video profiles. The video decoder is designed to be extremely power efficient without sacrificing performance. The video decoder communicates with the memory controller through the video DMA which supports a variety of memory format output options. For low-power operations, the video decoder can operate at the lowest possible frequency while maintaining real-time decoding using dynamic frequency scaling techniques.

Video decode standards supported: H.265 (HEVC), H.264, VP9, VP8, AV1, MPEG-4, MPEG-2, and VC-1.

**Table 5: Supported Video Decode Streams**

| Standard        | Profile(s)                                                                  | Resolution (Maximum Number of Streams)              | Throughput<br>MPix/s (Up to) | Maximum<br>Cumulative<br>Bitrate (Mbps) |

|-----------------|-----------------------------------------------------------------------------|-----------------------------------------------------|------------------------------|-----------------------------------------|

| H.264           | Baseline, Main, High                                                        | 4K30 (1)   1080p60 (3)   1080p30 (7)                | 450                          | 115                                     |

|                 | High 444, High 444 Predictive,<br>MVC (per view considering<br>two views) * | 1x1080p60   3x 1080p30                              | 225                          | 100                                     |

| H.265<br>(HEVC) | Main, Main10                                                                | 4K60 (1)   4K30 (2)   1080p60 (5)  <br>1080p30 (11) | 690                          | 150                                     |

|                 | Main 444, Main 444 10, MV<br>(per view)                                     | 4K30 (1)   1080p60 (2)   1080p30 (5)                | 340                          | 100                                     |

| AV1             | Main Profile                                                                | 4K60 (1)   4K30 (2)   1080p60 (5)  <br>1080p30 (10) | 625                          | 75                                      |

| VP9             | Profile 0, Profile 2                                                        | 4K60 (1)   4K30 (2)   1080p60 (5)  <br>1080p30 (10) | 625                          | 100                                     |

<sup>\*</sup> Maximum throughput half for YUV444 – as compared to YUV420

# 1.9.2 Video Image Compositor (VIC)

VIC implements various 2D image and video operations in a power-efficient manner. It handles various system UI scaling, blending, rotation operations, video post-processing functions needed during video playback, and advanced de-noising functions used for camera capture.

### Features:

- Color Decompression

- High-quality Deinterlacing

- Inverse Teleciné

- Temporal Noise Reduction

- o New Bilateral Filter as spatial filter

- o Improved TNR3 algorithm

- Scaling

- Color Conversion

- Memory Format Conversion

- Blend/Composite

- 2D Bit BLIT operation

- Rotation

- Geometry Transform Processing

- o Programmable nine-points controlled warp patch for distortion correction

- Real-time on-the-fly position generation from sparse warp map surface

- Pincushion/barrel/moustache distortion correction

- o Distortion correction of 180- and 360-degree wide FOV lens

- o Scene perspective orientation adjustment with IPT

- o Full warp map capability

- Non-fixed Patch size with 4x4 regions

- External Mask bit map surface

# 1.9.3 Audio Processing Engine (APE)

The Audio Processing Engine (APE) is a self-contained unit with dedicated audio clocking that enables Ultra Low Power (ULP) audio processing. Software based post processing effects enable the ability to implement custom audio algorithms.

#### Features:

- 96 KB Audio RAM

- Audio Hub (AHUB) I/O Modules

- o 2x I2S/3x DMIC/2x DSPK Audio Hub (AHUB) Internal Modules

- Sample Rate converter

- Mixer

- Audio Multiplexer

- Audio De-multiplexer

- Master Volume Controller

- Multi-Channel IN/OUT

- Digital Audio Mixer: 10-in/5-out

- Up to eight channels per stream

- Simultaneous Multi-streams

- Flexible stream routing

- Parametric equalizer: up to 12 bands

- Low latency sample rate conversion (SRC) and high-quality asynchronous sample rate conversion (ASRC)

### 1.9.4 High-Definition Audio (HDA)

#### Standard

Intel High-Definition Audio Specification Revision 1.0a

The Jetson Orin Nano implements an industry-standard High-Definition Audio (HDA) controller. This controller provides a multi-channel audio path to the HDMI interface. The HDA block also provides an HDA-compliant serial interface to an audio codec. A maximum of four streams are supported.

#### Features:

- Supports HDMI 2.1 and DP1.4

- Support up to two audio streams for use with HDMI/DP

- Supports striping of audio out across 1,2,4<sup>[a]</sup> SDO lines

- Supports DVFS with maximum latency up to 208 µs for eight channels

- Supports Multi-Stream Transport (MST)

- Audio Format Support

- o Uncompressed Audio (LPCM): 16/20/24 bits at 32/44.1/48/88.2/96/176.4/192<sup>[b]</sup> kHz

- Compressed Audio format: AC3, DTS5.1, MPEG1, MPEG2, MP3, DD+, MPEG2/4 AAC, TrueHD, DTS-HD

[a] Four SDO lines: cannot support one stream, 48 kHz, 16-bits, two channels; for this case, use a one or two SDO line configuration.

[b] DP protocol sample frequency limitation: cannot support >96 kHz; that is, it does not support 176.4 kHz and 196 kHz.

# 1.10 Interface Descriptions

The following sections outline the interfaces available on the Jetson Orin Nano module and details the module pins used to interact with and control each interface. See the *Jetson Orin Nano* and *Jetson Orin NX Series Product Design Guide* for complete functional descriptions, programming guidelines, and register listings for each of these blocks.

# 1.10.1 Universal Serial Bus (USB)

| Standard                                                                               | Notes                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Universal Serial Bus Specification Revision 3.2 Gen1 and Gen2                          | -                                                                                                                                                                                                                       |

| Universal Serial Bus Specification Revision 2.0                                        | <ul> <li>Modes: Host and Device (Only USB 2.0 port USB0 supports RCM, Host, Device Mode.All other ports are Host only)</li> <li>Speeds: Low, Full, and High</li> <li>USB Battery Charging 1.2 Specifications</li> </ul> |

| Enhanced Host Controller Interface Specification for Universal Serial Bus revision 1.0 | -                                                                                                                                                                                                                       |

An xHCI/Device controller (named XUSB) supports the xHCI programming model for scheduling transactions and interface managements as a host that natively supports USB 3.2, USB 2.0, and USB 1.1 transactions with its USB 3.2 and USB 2.0 interfaces. The XUSB controller supports USB 2.0 L1 and L2 (suspend) link power management and USB 3.2 U1, U2, and U3 (suspend) link power managements. The XUSB controller supports remote wakeup, wake on connect, wake on disconnect, and wake on overcurrent in all power states, including sleep mode.

### 1.10.1.1 USB 2.0 Operation

Each USB 2.0 port (3x) operates in USB 2.0 high-speed mode when connecting directly to a USB 2.0 peripheral and operates in USB 1.1 full- and low-speed modes when connecting directly to a USB 1.1 peripheral. When operating in High-Speed mode, each USB 2.0 port is allocated with one High-Speed unit bandwidth. Approximately a 480 Mb/s bandwidth is allocated to each USB 2.0 port. All USB 2.0 ports operating in full- or low-speed modes share one full- and low-speed bus instance, which means 12 Mb/s theoretical bandwidth is distributed across these ports.

Table 6: USB 2.0 Pin Descriptions

| Pin# | Signal Name | Description          | Direction | Pin Type |

|------|-------------|----------------------|-----------|----------|

| 109  | USB0_D_N    | USB 2.0 Port 0 Data- | Bidir     | USB PHY  |

| 111  | USB0_D_P    | USB 2.0 Port 0 Data+ | Bidir     | USB PHY  |

| 115  | USB1_D_N    | USB 2.0 Port 1 Data- | Bidir     | USB PHY  |

| 117  | USB1_D_P    | USB 2.0 Port 1 Data+ | Bidir     | USB PHY  |

| 121  | USB2_D_N    | USB 2.0 Port 2 Data- | Bidir     | USB PHY  |

| 123  | USB2_D_P    | USB 2.0 Port 2 Data+ | Bidir     | USB PHY  |

### 1.10.1.2 USB 3.2 Operation

In host mode, the USB3.2 host controller supports Gen2 Super Speed+, 10 Gbps transfer rates. In device mode, the USB3.2 controller supports Gen1 Super Speed.

**Note:** There is an internal USB 3.2 hub for ports 0 and 1. The hub supports 10Gbps bandwidth which would be shared between the two ports.

Table 7: USB 3.2 Pin Descriptions

| Pin# | Signal Name | Description                       | Direction | Pin Type   |

|------|-------------|-----------------------------------|-----------|------------|

| 161  | USBSS0_RX_N | USB SS Receive- (USB 3.2 Ctrl #0) | Input     | USB SS PHY |

| 163  | USBSS0_RX_P | USB SS Receive+ (USB 3.2 Ctrl #0) | Input     | USB SS PHY |

| Pin# | Signal Name | Description                        | Direction | Pin Type   |

|------|-------------|------------------------------------|-----------|------------|

| 166  | USBSS0_TX_N | USB SS Transmit- (USB 3.2 Ctrl #0) | Output    | USB SS PHY |

| 168  | USBSS0_TX_P | USB SS Transmit+ (USB 3.2 Ctrl #0) | Output    | USB SS PHY |

| 39   | USBSS1_RX_N | USB SS Receive- (USB 3.2 Ctrl #1)  | Input     | USB SS PHY |

| 41   | USBSS1_RX_P | USB SS Receive+ (USB 3.2 Ctrl #1)  | Input     | USB SS PHY |

| 45   | USBSS1_TX_N | USB SS Transmit- (USB 3.2 Ctrl #1) | Output    | USB SS PHY |

| 47   | USBSS1_TX_P | USB SS Transmit+ (USB 3.2 Ctrl #1) | Output    | USB SS PHY |

| 51   | USBSS2_RX_N | USB SS Receive- (USB 3.2 Ctrl #2)  | Input     | USB SS PHY |

| 53   | USBSS2_RX_P | USB SS Receive+ (USB 3.2 Ctrl #2)  | Input     | USB SS PHY |

| 57   | USBSS2_TX_N | USB SS Transmit- (USB 3.2 Ctrl #2) | Output    | USB SS PHY |

| 59   | USBSS2_TX_P | USB SS Transmit+ (USB 3.2 Ctrl #2) | Output    | USB SS PHY |

# 1.10.2 PCI Express (PCIe)

| Standard                                    | Notes |

|---------------------------------------------|-------|

| PCI Express Base Specification Revision 4.0 |       |

The Jetson Orin Nano module integrates four PCle controllers supporting:

- Connections to two interfaces, 3 x1 (or 1 x2 + 1 x1) + 1 x4 GEN3.

- x1 and x2 (supports Root Port only), x4 (supports Root Port or Endpoint modes) upstream and downstream AXI interfaces that serve as the control path from the Jetson Orin Nano to the external PCIe device.

- Gen3 (8 GT/s) supported on all controllers/lanes.

- Four PCle controllers, seven lanes for a total of 56GT/s.

- Controller #0 can operate in x1, x2, or x4 mode.

- Controller #1 operates in x1 mode only.

- Controller #2 can operate in x1, x2 mode.

- Controller #3 is available if Controller #2 is not used or only used in x1 mode. In these cases, Controller #3 can operate in x1 mode.

### **Table 8: PCIe Pin Descriptions**

| Pin# | Signal Name | Description                              | Direction | Pin Type |

|------|-------------|------------------------------------------|-----------|----------|

| 131  | PCIE0_RX0_N | PCIe 0 Receive 0– (PCIe Ctrl #4 Lane 0)  | Input     | PCIe PHY |

| 133  | PCIE0_RX0_P | PCIe 0 Receive 0+ (PCIe Ctrl #4 Lane 0)  | Input     | PCIe PHY |

| 137  | PCIE0_RX1_N | PCIe 0 Receive 1– (PCIe Ctrl #4 Lane 1)  | Input     | PCIe PHY |

| 139  | PCIE0_RX1_P | PCIe 0 Receive 1+ (PCIe Ctrl #4 Lane 1)  | Input     | PCIe PHY |

| 149  | PCIE0_RX2_N | PCIe 0 Receive 2– (PCIe Ctrl #4 Lane 2)  | Input     | PCIe PHY |

| 151  | PCIE0_RX2_P | PCIe 0 Receive 2+ (PCIe Ctrl #4 Lane 2)  | Input     | PCIe PHY |

| 155  | PCIE0_RX3_N | PCIe 0 Receive 3– (PCIe Ctrl #4 Lane 3)  | Input     | PCIe PHY |

| 157  | PCIE0_RX3_P | PCIe 0 Receive 3+ (PCIe Ctrl #4 Lane 3)  | Input     | PCIe PHY |

| 134  | PCIE0_TX0_N | PCIe 0 Transmit 0- (PCIe Ctrl #4 Lane 0) | Output    | PCIe PHY |

| 136  | PCIE0_TX0_P | PCIe 0 Transmit 0+ (PCIe Ctrl #4 Lane 0) | Output    | PCIe PHY |

| Pin# | Signal Name                  | Description                                                                                                                                              | Direction | Pin Type        |

|------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| 140  | PCIE0_TX1_N                  | PCIe 0 Transmit 1– PCIe Ctrl #4 Lane 1)                                                                                                                  | Output    | PCIe PHY        |

| 142  | PCIE0_TX1_P                  | PCIe 0 Transmit 1+ (PCIe Ctrl #4 Lane 1)                                                                                                                 | Output    | PCIe PHY        |

| 148  | PCIE0_TX2_N                  | PCIe 0 Transmit 2– (PCIe Ctrl #4 Lane 2)                                                                                                                 | Output    | PCIe PHY        |

| 150  | PCIE0_TX2_P                  | PCIe 0 Transmit 2+ (PCIe Ctrl #4 Lane 2)                                                                                                                 | Output    | PCIe PHY        |

| 154  | PCIE0_TX3_N                  | PCle 0 Transmit 3– (PCle Ctrl #4 Lane 3)                                                                                                                 | Output    | PCIe PHY        |

| 156  | PCIE0_TX3_P                  | PCIe 0 Transmit 3+ (PCIe Ctrl #4 Lane 3)                                                                                                                 | Output    | PCIe PHY        |

| 181  | PCIE0_RST*                   | PCIe 0 Reset (PCIe Ctrl #4). 4.7k $\Omega$ pull-up to 3.3V on the module. Output when Orin Nano is Root Port or input when Orin Nano is Endpoint.        | Bidir     | Open Drain 3.3V |

| 180  | PCIE0_CLKREQ*                | PCIE 0 Clock Request (PCIe Ctrl #4). 47k $\Omega$ pull-up to 3.3V on the module. Input when Orin Nano is Root Port or output when Orin Nano is Endpoint. | Bidir     | Open Drain 3.3V |

| 160  | PCIE0_CLK_N                  | PCIe #0 Reference Clock- (reference clock input when Orin Nano is an Endpoint).                                                                          | Bidir     | PCIe PHY        |

| 162  | PCIE0_CLK_P                  | PCIe #0 Reference Clock+ (reference clock input when Orin Nano is an Endpoint).                                                                          | Bidir     | PCIe PHY        |

| 167  | PCIE1_RX0_N                  | PCIe 1 Receive 0- (PCIe Ctrl #1 Lane 0)                                                                                                                  | Input     | PCIe PHY        |

| 169  | PCIE1_RX0_P                  | PCIe 1 Receive 0+ (PCIe Ctrl #1 Lane 0)                                                                                                                  | Input     | PCIe PHY        |

| 172  | PCIE1_TX0_N                  | PCIe 1 Transmit 0– (PCIe Ctrl #1 Lane 0)                                                                                                                 | Output    | PCIe PHY        |

| 174  | PCIE1_TX0_P                  | PCle 1 Transmit 0+ (PCle Ctrl #1 Lane 0)                                                                                                                 | Output    | PCIe PHY        |

| 183  | PCIE1_RST*                   | PCIe 1 Reset (PCIe Ctrl #1). 4.7k $\Omega$ pull-up to 3.3V on the module.                                                                                | Output    | PCIe PHY        |

| 182  | PCIE1_CLKREQ*                | PCIe 1 Clock Request (PCIe Ctrl #1). 47k $\Omega$ pull-up to 3.3V on the module.                                                                         | Bidir     | PCIe PHY        |

| 173  | PCIE1_CLK_N                  | PCIe 1 Reference Clock- (PCIe Ctrl #1)                                                                                                                   | Output    | PCIe PHY        |

| 175  | PCIE1_CLK_P                  | PCIe 1 Reference Clock+ (PCIe Ctrl #1)                                                                                                                   | Output    | PCIe PHY        |

| 179  | PCIE_WAKE*                   | PCIe Wake. $47k\Omega$ pull-up to 3.3V on the module.                                                                                                    | Bidir     | Open Drain 3.3V |

| 40   | PCIE2_RX0_N                  | PCIe 2 Receive 0- (PCIe Ctrl #7 Lane 0)                                                                                                                  | Input     | PCIe PHY        |

| 42   | PCIE2_RX0_P                  | PCIe 2 Receive 0+ (PCIe Ctrl #7 Lane 0)                                                                                                                  | Input     | PCIe PHY        |

| 46   | PCIE2_TX0_N                  | PCle 2 Transmit 0- (PCle Ctrl #7 Lane 0)                                                                                                                 | Output    | PCIe PHY        |

| 48   | PCIE2_TX0_P                  | PCle 2 Transmit 0+ (PCle Ctrl #7 Lane 0)                                                                                                                 | Output    | PCIe PHY        |

| 58   | PCIE2_RX1_N<br>(PCIE3_RX0_N) | PCIe 2 Receive 1– (PCIe Ctrl #7 Lane 1) or PCIe 3 Receive 0– (PCIe Ctrl #9 Lane 0)                                                                       | Input     | PCIe PHY        |

| 60   | PCIE2_RX1_P<br>(PCIE3_RX0_P) | PCIe 2 Receive 1+ (PCIe Ctrl #7 Lane 1) or PCIe 3 Receive 0+ (PCIe Ctrl #9 Lane 0)                                                                       | Input     | PCIe PHY        |

| 64   | PCIE2_TX1_N<br>(PCIE3_TX0_N) | PCIe 2 Transmit 1– (PCIe Ctrl #7 Lane 1) or PCIe 3 Transmit 0– (PCIe Ctrl #9 Lane 0)                                                                     | Output    | PCIe PHY        |

| 66   | PCIE2_TX1_P<br>(PCIE3_TX0_P) | PCIe 2 Transmit 1+ (PCIe Ctrl #7 Lane 1) or PCIe 3 Transmit 0+ (PCIe Ctrl #9 Lane 0)                                                                     | Output    | PCIe PHY        |

| 52   | PCIE2_CLK_N                  | PCIe 2 Reference Clock- (PCIe Ctrl #7)                                                                                                                   | Output    | PCIe PHY        |

| Pin# | Signal Name   | Description                                                                      | Direction | Pin Type |

|------|---------------|----------------------------------------------------------------------------------|-----------|----------|

| 54   | PCIE2_CLK_P   | PCIe 2 Reference Clock+ (PCIe Ctrl #7)                                           | Output    | PCle PHY |

| 219  | PCIE2_RST*    | PCIe 2 Reset (PCIe Ctrl #7). 4.7kΩ pull-up to 3.3V on the module.                | Output    | PCIe PHY |

| 221  | PCIE2_CLKREQ* | PCIe 2 Clock Request (PCIe Ctrl #7). 47k $\Omega$ pull-up to 3.3V on the module. | Bidir     | PCIe PHY |

| 229  | PCIE3_CLK_P   | PCIe 3 Reference Clock- (PCIe Ctrl #9)                                           | Output    | PCIe PHY |

| 227  | PCIE3_CLK_N   | PCIe 3 Reference Clock+ (PCIe Ctrl #9)                                           | Output    | PCIe PHY |

| 223  | PCIE3_RST*    | PCIe 3 Reset (PCIe Ctrl #9). 4.7kΩ pull-up to 3.3V on the module.                | Output    | PCIe PHY |

| 225  | PCIE3_CLKREQ* | PCIe 3 Clock Request (PCIe Ctrl #9). 47k $\Omega$ pull-up to 3.3V on the module. | Bidir     | PCIe PHY |

See the Jetson Orin NX and Jetson Orin Nano Product Design Guide for supported USB 3.2/PCIe configuration and connection examples.

# 1.10.3 Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) controller allows a duplex, synchronous, serial communication between the controller and external peripheral devices; it supports both Master and Slave modes of operation on the SPI bus. See the *Jetson Orin NX* and *Jetson Orin Nano Product Design Guide* for more information.

#### Features:

- 2x SPI Interface

- Master mode operation

- O All transfer modes (Mode 0, Mode 1, Mode 2, Mode 3) supported for both transmit and receive transactions

- FIFO Size: 64 x 32 bits

- Programmable packet sizes of 4 to 32 bits

- Programmable clock phase and polarity

- Programmable delay between consecutive transfers

- Chip select controllable by software or generated by hardware on packet boundaries

**Table 9: SPI Mode Descriptions**

| SPI Mode | Clock<br>Polarity | Clock<br>Phase | SCK<br>Inactive State | Data Latch In                            | Data Latch Out                            |

|----------|-------------------|----------------|-----------------------|------------------------------------------|-------------------------------------------|

| 0        | 0                 | 0              | Low                   | Latched IN on the positive edge of clock | Latched OUT on the negative edge of clock |

| 1        | 0                 | 1              | Low                   | Latched IN on the negative edge of clock | Latched OUT on the positive edge of clock |

| 2        | 1                 | 0              | High                  | Latched IN on the negative edge of clock | Latched OUT on the positive edge of clock |

| 3        | 1                 | 1              | High                  | Latched IN on the positive edge of clock | Latched OUT on the negative edge of clock |

**Table 10: SPI Pin Descriptions**

| Pin# | Signal Name | Description                 | Direction | Pin Type    |

|------|-------------|-----------------------------|-----------|-------------|

| 91   | SPI0_SCK    | SPI 0 Clock                 | Bidir     | CMOS – 1.8V |

| 89   | SPI0_MOSI   | SPI 0 Master Out / Slave In | Bidir     | CMOS - 1.8V |

| 93   | SPI0_MISO   | SPI 0 Master In / Slave Out | Bidir     | CMOS – 1.8V |

| 95   | SPI0_CS0*   | SPI 0 Chip Select 0         | Bidir     | CMOS - 1.8V |

| 97   | SPI0_CS1*   | SPI 0 Chip Select 1         | Bidir     | CMOS – 1.8V |

| 106  | SPI1_SCK    | SPI 1 Clock                 | Bidir     | CMOS - 1.8V |

| 104  | SPI1_MOSI   | SPI 1 Master Out / Slave In | Bidir     | CMOS - 1.8V |

| 108  | SPI1_MISO   | SPI 1 Master In / Slave Out | Bidir     | CMOS - 1.8V |

| 110  | SPI1_CS0*   | SPI 1 Chip Select 0         | Bidir     | CMOS - 1.8V |

| 112  | SPI1_CS1*   | SPI 1 Chip Select 1         | Bidir     | CMOS - 1.8V |

## 1.10.4 Universal Asynchronous Receiver/Transmitter (UART)

The UART controller provides serial data synchronization and data conversion (parallel-to-serial and serial-to-parallel) for both receiver and transmitter sections. Synchronization for serial data stream is accomplished by adding start and stop bits to the transmit data to form a data character. Data integrity is accomplished by attaching a parity bit to the data character. The parity bit can be checked by the receiver for any transmission bit errors.

Note:

The UART receiver input has low baud rate tolerance in 1-stop bit mode. External devices must use two stop bits. In 1-stop bit mode, the UART receiver can lose sync between the receiver and the external transmitter resulting in data errors/corruption. In 2-stop bit mode, the extra stop bit allows the UART receiver logic to align properly with the UART transmitter.

### Features:

- 3x UART Interface

- Synchronization for the serial data stream with start and stop bits to transmit data and form a data character

- Supports both 16450- and 16550-compatible modes. Default mode is 16450

- Device clock up to 200 MHz, baud rate of 12.5 Mbits/second

- Support for word lengths from five to eight bits, an optional parity bit and one or two stop bits

- Support for modem control inputs

- · Auto sense baud detection

- · Timeout interrupts to indicate if the incoming stream stopped

- Priority interrupts mechanism

- Flow control support on RTS and CTS

- SIR encoding/decoding (3/16 or 4/16 baud pulse widths to transmit bit zero)

### **Table 11: UART Pin Descriptions**

| Pin# | Signal Name | Description             | Direction | Pin Type    |

|------|-------------|-------------------------|-----------|-------------|

| 99   | UART0_TXD   | UART #0 Transmit        | Output    | CMOS - 1.8V |

| 101  | UART0_RXD   | UART #0 Receive         | Input     | CMOS - 1.8V |

| 103  | UART0_RTS*  | UART #0 Request to Send | Output    | CMOS - 1.8V |

| 105  | UART0_CTS*  | UART #0 Clear to Send   | Input     | CMOS - 1.8V |

| Pin # | Signal Name | Description             | Direction | Pin Type    |

|-------|-------------|-------------------------|-----------|-------------|

| 203   | UART1_TXD   | UART #1 Transmit        | Output    | CMOS – 1.8V |

| 205   | UART1_RXD   | UART #1 Receive         | Input     | CMOS – 1.8V |

| 207   | UART1_RTS*  | UART #1 Request to Send | Output    | CMOS – 1.8V |

| 209   | UART1_CTS*  | UART #1 Clear to Send   | Input     | CMOS – 1.8V |

| 236   | UART2_TXD   | UART #2 Transmit        | Output    | CMOS - 1.8V |

| 238   | UART2_RXD   | UART #2 Receive         | Input     | CMOS – 1.8V |

### 1.10.5 Controller Area Network (CAN)

| Standard         | Notes                                                        |

|------------------|--------------------------------------------------------------|

| ISO/DIS 16845-2  | CAN conformance test                                         |

| ISO 11898-1:2015 | Data link layer and physical signaling; CAN FD Frame formats |

| ISO 11898-4:2004 | Time-triggered communication                                 |

The Jetson Orin Nano integrates the Bosch Time-Triggered Controller Area Network (M\_TTCAN) controller version 3.2.0. One independent CAN port/channel supports connectivity to one CAN network. Each port instantiates the Bosch M\_TTCAN module, a message RAM module, an APB slave interface module, interrupt aggregator, time-triggered control module, and a wake detect module. All M\_TTCAN external modules have direct connections to M\_TTCAN except for the wake detect module.

#### Features:

- Standard frame and extended frame transmission/reception enable.

- Transfer rate: programmable bit rates up to 15 Mbps.

- 0 8-byte data length, with the ability to receive the first 8 bytes when data length coding is > 8 Bytes.

- 32 message buffers per channel.

- · Prioritization of transmit buffers.

- Receive/transmit history list function.

- Automatic block transmission function.

- Multi-buffer receives block function.

- Flexible maskable identifier filter support for two 32-bit, or four 16-bit, or eight 8-bit filters for each channel

- Programmable data bit time, communication baud rate, and sample point.

- As an example, the following sample-point configurations can be configured: 66.7%, 70.0%, 75.0%, 80.0%, 81.3%, 85.0%, and 87.5%

- o Baud rates in the range of 10 kbps up to 1000 kbps can be configured.

- Enhanced features:

- o Each message buffer can be configured to operate as a transmit or a receive message buffer.

- o Transmission priority is controlled by the identifier or by mailbox number (selectable).

- A transmission request can be aborted by clearing the dedicated Transmit-Request flag of the concerned message buffer.

- Automatic block transmission (ABT) operation mode.

- Time stamp function for CAN channels 0 to n in collaboration with timers.

- Release from bus-off state by software.

- Wake-up with integrated low-pass filter (debounce) option to prevent short glitches on CAN bus, through CAN receive signal toggling from CAN transceiver.

- o For normal operation (after wake) there is a digital filter in the CAN controller.

- Listen-only mode to monitor CAN bus.

- Wake-up signal to both internal and external (either interrupt signal or GPIO) to initiate power up if needed.

- Ready to receive the first CAN message within 10ms of wake event generated by the CAN master.

- Ready to transmit the first CAN message within 50ms of wake event generated by the CAN master.

- Loop back for self-test

#### **Table 12: CAN Pin Descriptions**

| Pin# | Signal Name | Description  | Direction | Pin Type    |

|------|-------------|--------------|-----------|-------------|

| 145  | CAN_TX      | CAN Transmit | Output    | CMOS - 3.3V |

| 143  | CAN_RX      | CAN Receive  | Input     | CMOS - 3.3V |

# 1.10.6 Inter-Chip Communication (I<sup>2</sup>C)

| Standard                                          | Notes                                  |

|---------------------------------------------------|----------------------------------------|

| NXP inter-IC-bus (I <sup>2</sup> C) specification | https://i2c.info/i2c-bus-specification |

This general purpose I<sup>2</sup>C controller allows system expansion for I<sup>2</sup>C-based devices as defined in the NXP inter-IC-bus (I<sup>2</sup>C) specification. The I<sup>2</sup>C bus supports serial device communications to multiple devices. (4x I<sup>2</sup>C) The I<sup>2</sup>C controller handles clock source negotiation, speed negotiation for standard and fast devices, 7-bit slave address support according to the I<sup>2</sup>C protocol and supports master and slave modes of operation.

The I<sup>2</sup>C controller supports the following operating modes:

- Master Standard-mode (up to 100 Kbit/s), Fast-mode (up to 400 Kbit/s), Fast-mode plus (Fm+, up to 1 Mbit/s).

- Slave Standard-mode (up to 100 Kbit/s), Fast-mode (up to 400 Kbit/s), Fast-mode plus (Fm+, up to 1 Mbit/s).

### **Table 13: I2C Pin Descriptions**

| Pin # | Signal Name | Description                                                    | Direction | Pin Type          |

|-------|-------------|----------------------------------------------------------------|-----------|-------------------|

| 185   | I2C0_SCL    | General I2C 0 Clock. 1.5kΩ pull-up to 3.3V on module.          | Bidir     | Open Drain – 3.3V |

| 187   | I2C0_SDA    | General I2C 0 Data. 1.5kΩ pull-up to 3.3V on the module.       | Bidir     | Open Drain – 3.3V |

| 189   | I2C1_SCL    | General I2C 1 Clock. 2.2kΩ pull-up to 3.3V on the module.      | Bidir     | Open Drain – 3.3V |

| 191   | I2C1_SDA    | General I2C 1 Data. 2.2kΩ pull-up to 3.3V on the module.       | Bidir     | Open Drain – 3.3V |

| 232   | I2C2_SCL    | General I2C 2 Clock. 2.2kΩ pull-up to 1.8V on the module.      | Bidir     | Open Drain – 1.8V |

| 234   | I2C2_SDA    | General I2C 2 Data. 2.2kΩ pull-up to 1.8V on the module.       | Bidir     | Open Drain – 1.8V |

| 213   | CAM_I2C_SCL | Camera I2C Clock. 2.2kΩ pull-up to 3.3V on the module.         | Bidir     | Open Drain – 3.3V |

| 215   | CAM_I2C_SDA | Camera I2C Data. $2.2k\Omega$ pull-up to $3.3V$ on the module. | Bidir     | Open Drain – 3.3V |

# 1.10.7 Inter-IC Sound (I<sup>2</sup>S)

| Standard                                        |

|-------------------------------------------------|

| Inter-IC Sound (I <sup>2</sup> S) specification |

The I<sup>2</sup>S controller transports streaming audio data between system memory and an audio codec. The I<sup>2</sup>S controller supports I<sup>2</sup>S format, left-justified mode format, right-justified mode format, and DSP mode format, as defined in the Philips inter-IC-sound (I<sup>2</sup>S) bus specification.

The I<sup>2</sup>S and PCM (master and slave modes) interfaces support clock rates up to 24.5760 MHz.

The I²S controller supports point-to-point serial interfaces for the I²S digital audio streams. I²S-compatible products, such as compact disc players, digital audio tape devices, digital sound processors, and those with digital TV sound may be directly connected to the I²S controller. The controller also supports the PCM and telephony mode of data-transfer. Pulse-Code-Modulation (PCM) is a standard method used to digitize audio (particularly voice) patterns for transmission over digital communication channels. The Telephony mode is used to transmit and receive data to and from an external mono CODEC in a slot-based scheme of time-division multiplexing (TDM). The I²S controller supports Bidirectional audio streams and can operate in half-duplex or full-duplex mode.

#### Features:

- Basic I<sup>2</sup>S modes to be supported (I<sup>2</sup>S, RJM, LJM, and DSP) in both master and slave modes.

- PCM mode with short (one bit-clock wide) and long-fsync (two bit-clock wide) in both master and slave modes.

- NW-mode with independent slot-selection for both transmit and receive.

- TDM mode with flexibility in number of slots and slot(s) selection.

- Capability to drive-out a high-z outside the prescribed slot for transmission.

- Flow control for the external input/output stream.

**Table 14: I2S Pin Descriptions**

| Pin# | Signal Name | Description                       | Direction | Pin Type    |

|------|-------------|-----------------------------------|-----------|-------------|

| 199  | I2S0_SCLK   | I2S Audio Port 0 Clock            | Bidir     | CMOS - 1.8V |

| 197  | I2S0_FS     | I2S Audio Port 0 Left/Right Clock | Bidir     | CMOS - 1.8V |

| 193  | I2S0_DOUT   | I2S Audio Port 0 Data Out         | Output    | CMOS - 1.8V |

| 195  | I2S0_DIN    | I2S Audio Port 0 Data In          | Input     | CMOS - 1.8V |

| 226  | I2S1_SCLK   | I2S Audio Port 1 Clock            | Bidir     | CMOS - 1.8V |

| 224  | I2S1_FS     | I2S Audio Port 1 Left/Right Clock | Bidir     | CMOS - 1.8V |

| 220  | I2S1_DOUT   | I2S Audio Port 1 Data Out         | Output    | CMOS - 1.8V |

| 222  | I2S1_DIN    | I2S Audio Port 1 Data In          | Input     | CMOS - 1.8V |

### 1.10.8 Gigabit Ethernet

| Standard               | Notes        |

|------------------------|--------------|

| Gigabit Ethernet (GbE) | IEEE 802.3ab |

The on-module Ethernet controller supports:

- 10/100/1000 Gigabit Ethernet

- IEEE 802.3u Media Access Controller (MAC)

**Table 15: Gigabit Ethernet Pin Descriptions**

| Pin# | Signal Name | Description             | Direction | Pin Type |

|------|-------------|-------------------------|-----------|----------|

| 184  | GBE_MDI0_N  | GbE Transformer Data 0- | Bidir     | MDI      |

| 186  | GBE_MDI0_P  | GbE Transformer Data 0+ | Bidir     | MDI      |

| 190  | GBE_MDI1_N  | GbE Transformer Data 1– | Bidir     | MDI      |

| 192  | GBE_MDI1_P  | GbE Transformer Data 1+ | Bidir     | MDI      |

| 196  | GBE_MDI2_N  | GbE Transformer Data 2– | Bidir     | MDI      |

| Pin# | Signal Name  | Description                    | Direction | Pin Type |

|------|--------------|--------------------------------|-----------|----------|

| 198  | GBE_MDI2_P   | GbE Transformer Data 2+        | Bidir     | MDI      |

| 202  | GBE_MDI3_N   | GbE Transformer Data 3–        | Bidir     | MDI      |

| 204  | GBE_MDI3_P   | GbE Transformer Data 3+        | Bidir     | MDI      |

| 188  | GBE_LED_LINK | Ethernet Link LED (Green)      | Output    | -        |

| 194  | GBE_LED_ACT  | Ethernet Activity LED (Yellow) | Output    | -        |

### 1.10.9 Fan

The Jetson Orin Nano includes a Pulse Width Modulator (PWM) and Tachometer functionality to enable fan control as part of a thermal solution. The PWM controller is a frequency divider with a varying pulse width. The PWM runs off a device clock programmed in the Clock and Reset controller and can be any frequency up to the device clock maximum speed of 48 MHz. The PWM gets divided by 256 before being subdivided based on a programmable value.

# 1.10.10 Pulse Width Modulator (PWM)

Jetson Orin Nano has four PWM outputs. Each PWM output is based on a frequency divider whose pulse width varies. Each has a programmable frequency divider and a programmable pulse width generator. The PWM controller supports one PWM output for each of its four instances. Each instance is allocated a 64 KB independent address space.

Frequency division is a 13-bit programmable value, and pulse division is an 8-bit value. The PWM can run at a maximum frequency of up to 408 MHz. The PWM controller can source its clock from either CLK\_M or PLLP. CLK\_M (19.2 MHz) is derived from the OSC clock (38.4 MHz). PLLP operates at 408 MHz.

The PWM clock frequency is divided by 256 before subdividing it based on the programmable frequency division value to generate the required frequency for the PWM output. The maximum output frequency that can be achieved from this configuration is 408 MHz/256 = 1.6 MHz. This 1.6 MHz frequency can be further divided using the frequency divisor in PWM.

The OSC clock is the primary/default source for the PWM IP clock. For higher PWM output frequency requirements, PLLP is the clock source (up to 408 MHz).

**Table 16: PWM Pin Descriptions**