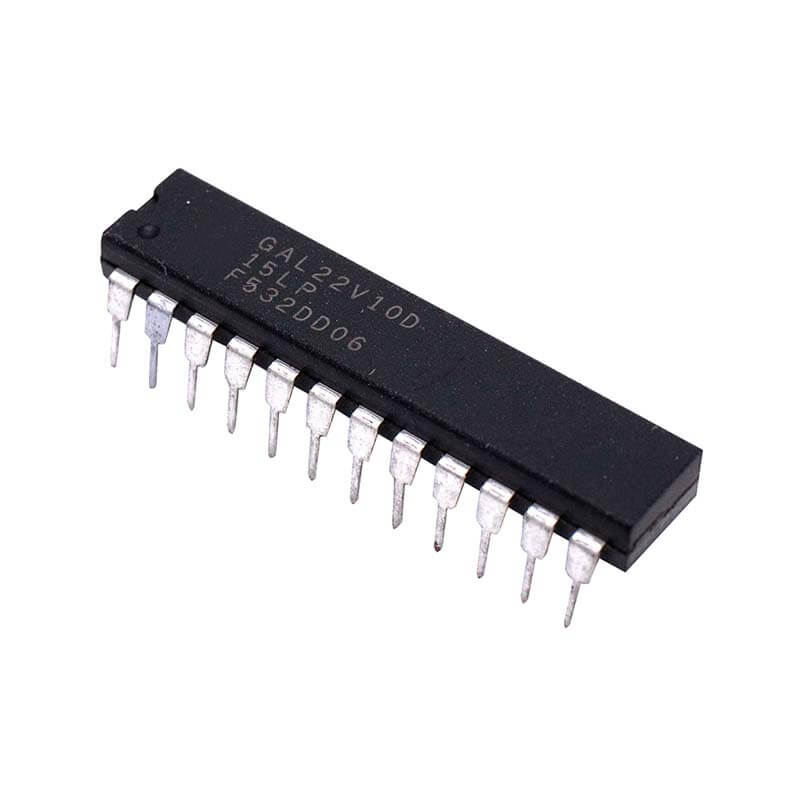

GAL22V10D-15LP Arreglo Lógico Programable DIP-24

$ 72.00

3 disponibles en TIENDA EN LÍNEA

INFORMACIÓN

La GAL22V10D-15LP Arreglo Lógico Programable es capaz de implementar funciones lógicas mediante un arreglo de compuertas AND y OR que pueden interconectarse internamente, lo esencial de este circuito integrado es que puede programarse con un dispositivo externo junto con un archivo que describe el hardware necesario en donde se define una función lógica deseada.

La GAL22V10D-15LP Arreglo Lógico Programable puede ser utilizado como decodificador, multiplexor, generadores de señales de temporización y circuitos de control entre otros.

ESPECIFICACIONES Y CARACTERÍSTICAS

- Matricula: GAL22V10

- Encapsulado: DIP-24

- Fmax = 250 Mhz

- Retardo de propagación de 4ns

- UltraMOS® Advanced CMOS Technology

- 3.5 ns máximo desde la entrada del Reloj hasta la salida de datos.

- Montaje: THT

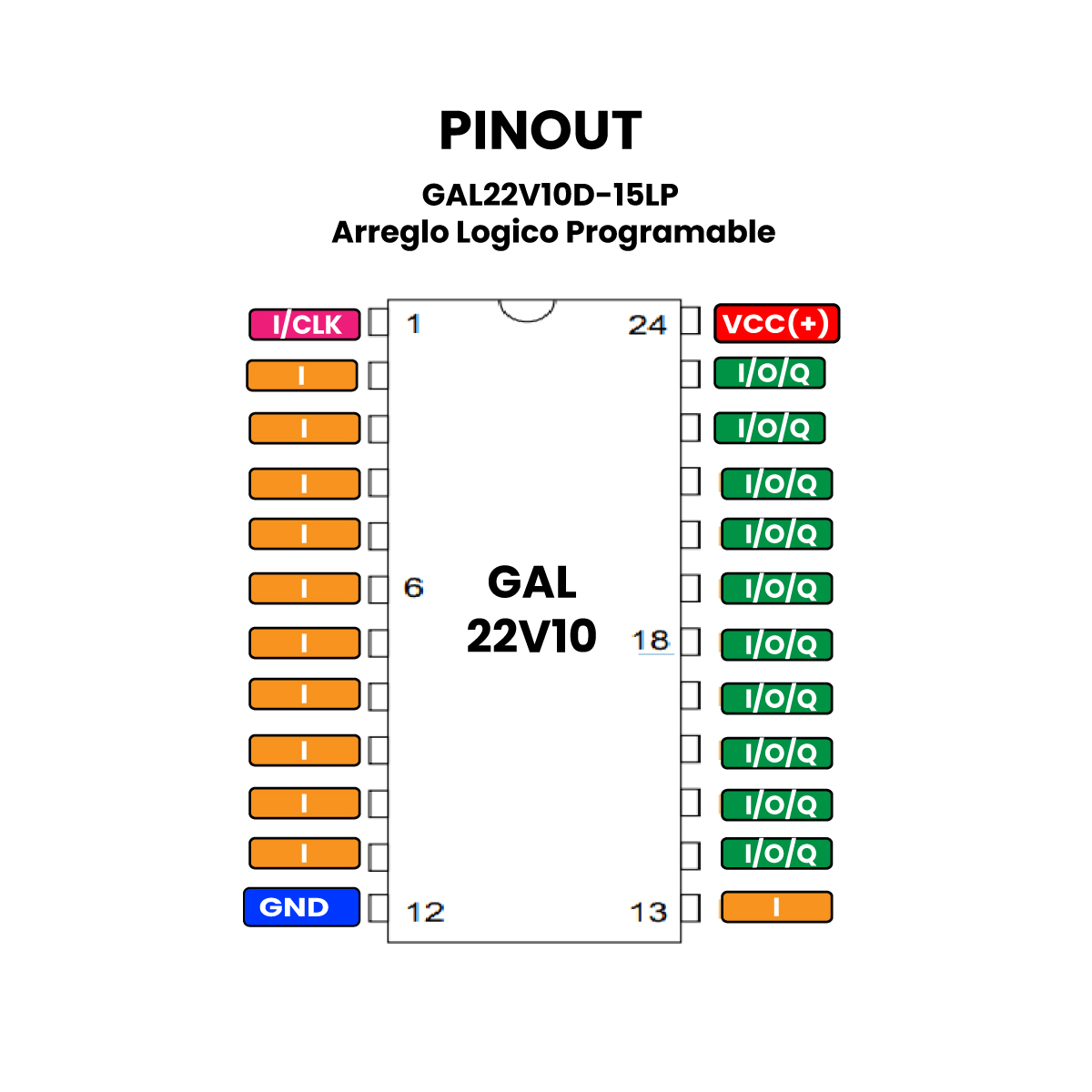

- Pines: 24

- Voltaje de alimentación (recomendado) Vcc : +4.75 a +5.25V

- Temperatura ambiente (recomendado) Tc : 0 a +75 °C

- Corriente de entrada Icc: 130 mA

- 64 bits de memoria reprogramable

- Pull-ups activos en todos los pines

- E 2 CELL Technology

- Lógica reconfigurable

- Células reprogramables

- Borrado eléctrico de alta velocidad (<100 ms)

- Retención de datos durante 20 años

Las aplicaciones incluyen:

- Control DMA

- Control de máquina de estados

- Procesamiento de gráficos de alta velocidad

- Actualización de velocidad lógica estándar

DOCUMENTACIÓN Y RECURSOS

INFORMACIÓN ADICIONAL

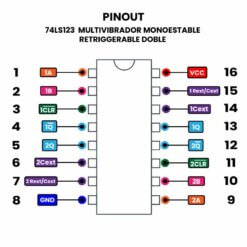

- EL GALL22V10D tiene 12 pines de entrada y 10 pines que se pueden configurar como entradas o salidas.

- Tiene varias velocidades de conmutación, de 25 a 4ns

- Cada salida es impulsada por una macrocélula lógica de salida (OLMC)

- Cada OMLC puede configurarse para que la salida sea inversora o no inversora.

- Se puede colocarse en modo registro o combinatorio.

- El modo registro cada macro célula utiliza activamente un D-flip-flop para mantener un estado bajo control de la entrada de datos desde la parte lógica de la macrocelda y el flanco ascendente de la señal de reloj.

- En el modo combinatorio se elimina el flip-flop de macrocelula y las salidas son impulsadas directamente por la lógica.

- En el modo combinatorio también se pueden cambiar dinámicamente entre entrada y salida según el termino del producto.

- Las combinaciones se establecen mediante una E 2 PROM .

- Los registros de salida se pueden precargar en un estado potencialmente no válido para que un programador GAL22V10 los pruebe. Las entradas y salidas incluyen pull-ups activos y son compatibles con la lógica transistor-transistor debido a los buffers de alta impedancia.

| Peso | 0.002 kg |

|---|---|

| Dimensiones | 0.43 × 3.1 × 0.64 cm |

Solo los usuarios registrados que hayan comprado este producto pueden hacer una valoración.

También te recomendamos…

INTERRUPTORES

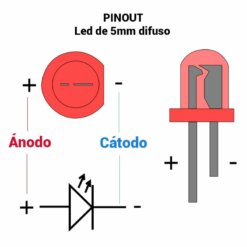

DIFUSOS & ULTRABRILLANTES

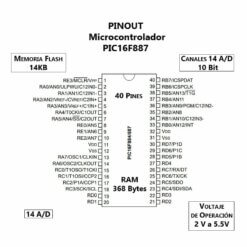

TAMBIÉN TE PODRÍA INTERESAR

COMPONENTES ELECTRÓNICOS

Valoraciones

No hay valoraciones aún.