-

×

RC522 Módulo RFID Lectura y Escritura

1 × $ 40.00

RC522 Módulo RFID Lectura y Escritura

1 × $ 40.00 -

×

Programador ESP32 ESP-WROOM-32

1 × $ 198.00

Programador ESP32 ESP-WROOM-32

1 × $ 198.00 -

×

RDM6300 Modulo lector RFID 125Khz

1 × $ 81.00

RDM6300 Modulo lector RFID 125Khz

1 × $ 81.00 -

×

Placa Perforada Tipo Protoboard 48 x 133 mm

1 × $ 17.00

Placa Perforada Tipo Protoboard 48 x 133 mm

1 × $ 17.00

Puede que estés interesado en…

-

Add

Flux Limpiador para Soldar 250 ML

$ 117.00

Flux Limpiador para Soldar 250 ML

$ 117.00 -

Add

Cloruro Férrico de 250 ML

$ 42.00

Cloruro Férrico de 250 ML

$ 42.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Soldadura en Pasta Mechanic 60 /200/ 500 g

$ 128.00 – $ 933.00

Soldadura en Pasta Mechanic 60 /200/ 500 g

$ 128.00 – $ 933.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Soldadura en Pasta Mechanic Jeringa/ Bote

$ 99.00 – $ 121.00

Soldadura en Pasta Mechanic Jeringa/ Bote

$ 99.00 – $ 121.00 -

Add

Pasta para Soldar ZJ-18 30g

$ 24.00

Pasta para Soldar ZJ-18 30g

$ 24.00

Subtotal: $ 336.00

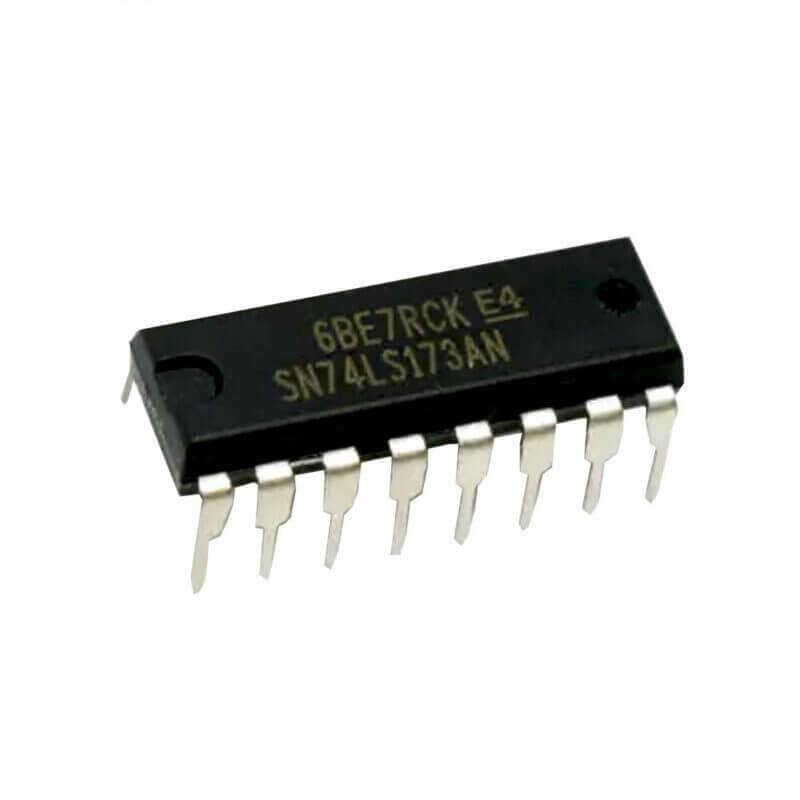

Programador ESP32 ESP-WROOM-32

Programador ESP32 ESP-WROOM-32  RDM6300 Modulo lector RFID 125Khz

RDM6300 Modulo lector RFID 125Khz  Placa Perforada Tipo Protoboard 48 x 133 mm

Placa Perforada Tipo Protoboard 48 x 133 mm

Valoraciones

No hay valoraciones aún.